# Introduction to Electronics and Computers Vol 1: Hardware

Draft XIV Brian Collett Physics Department Hamilton College Copyright Brian Collett 1997-2014

| Table of Contents                                            |     |

|--------------------------------------------------------------|-----|

| Chapter 1:Introduction                                       | 1   |

| Chapter 2:Basic electrical concepts                          | 3   |

| 2.1 The Properties of Charge                                 |     |

| 2.2 The physics of current flow                              |     |

| 2.2 The physics of current now                               | /   |

| Chapter 3:Simple Components                                  |     |

| <ul><li>3.1 Ideas of components</li><li>3.2 Ground</li></ul> |     |

|                                                              |     |

| 3.3 Wires.                                                   |     |

| 3.4 Switches.                                                |     |

| 3.5 Power Supplies                                           |     |

| <ul><li>3.6 Resistors</li></ul>                              |     |

| 5.7 Measuring instruments                                    | 20  |

| Chapter 4:Simple DC Circuits                                 | .23 |

| 4.1 Introduction                                             | 23  |

| 4.2 Simple Circuits                                          | 23  |

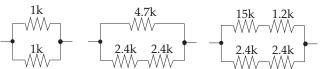

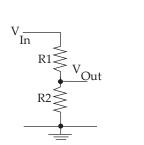

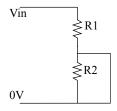

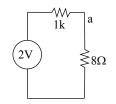

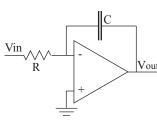

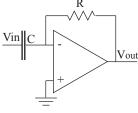

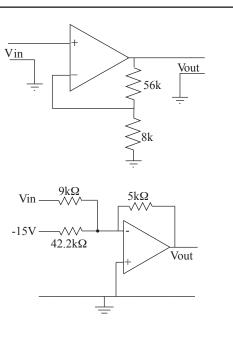

| 4.3 Resistors in Series                                      | 24  |

| 4.4 Resistors in parallel                                    |     |

| 4.5 Combinations of Series and Parallel                      | 26  |

| Chapter 5: Formal Analysis of DC Circuits                    | 33  |

| 5.1 Introduction                                             |     |

| 5.2 Kirchhoff's Laws                                         |     |

| 5.3 Method 1: Node analysis                                  |     |

| 5.4 *Method 2: Loop Analysis                                 |     |

| 5.5 Thévenin's Theory                                        |     |

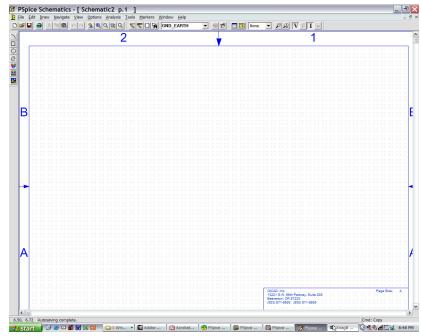

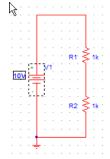

| 5.6 Solving Resistor Problems with PSpice                    |     |

|                                                              |     |

| Chapter 6: Time Varying                                      | 40  |

| Voltages                                                     |     |

| 6.1 Introduction                                             |     |

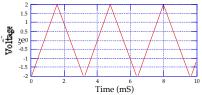

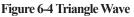

| 6.2 Periodic Voltages                                        |     |

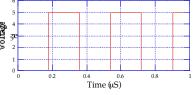

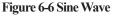

| 6.3 Sinewaves                                                |     |

| 6.4 A little helpful notation                                |     |

| 6.5 Time varying voltages and resistor circuits              |     |

| 6.6 Non-Sinusoidal Voltages                                  | 55  |

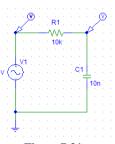

| Chapter 7: The Capacitor                                     | .55 |

| 7.1 Introduction                                             |     |

| 7.2 Resistor-capacitor circuits                              | 56  |

| 7.3 The Capacitor and the Sinewave                           | 58  |

| 7.4 RC Circuits and Sinewaves                                | 61  |

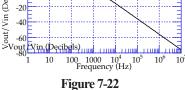

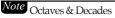

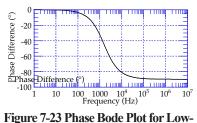

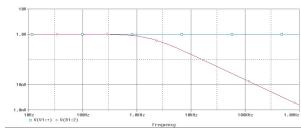

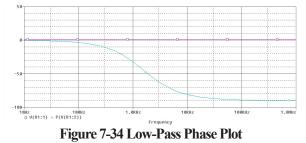

| 7.5 The Bode Plot                                            |     |

| 7.6 Thévenin and capacitors                                  | 64  |

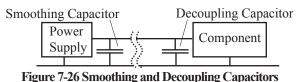

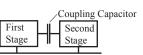

| 7.7 Common uses of capacitors                                | 64  |

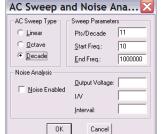

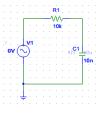

| 7.8 AC PSpice Simulations                                    | 66  |

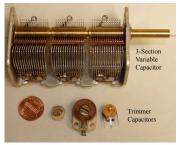

| 7.9 Real Capacitors                                          | 68  |

| Chantar 9.D. C. Exaguance                                    |     |

| Chapter 8:R-C Frequency<br>Selective Circuits                | 72  |

| 8.1 Introduction                                             |     |

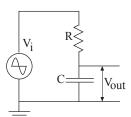

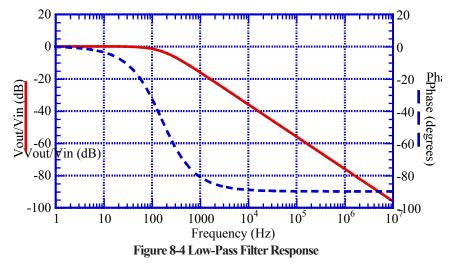

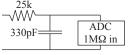

| 8.2 Low-pass Filter                                          |     |

| 0.2 20 m public inter                                        | , 5 |

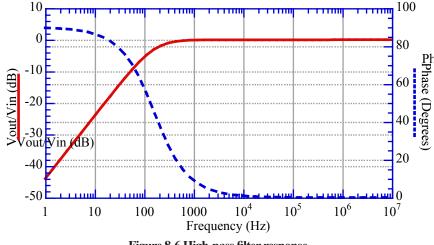

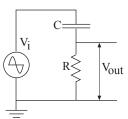

| 8.3 RC High-pass Filter                 |     |

|-----------------------------------------|-----|

| 8.4 Tone Controls                       |     |

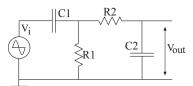

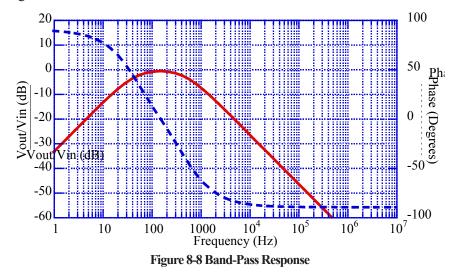

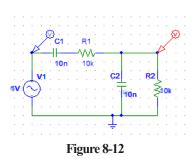

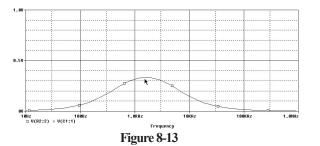

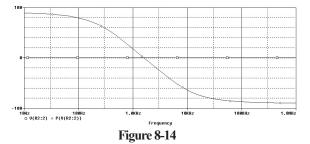

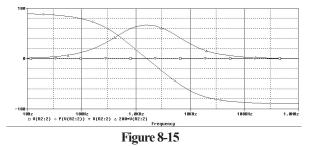

| 8.5 Bandpass Filter                     |     |

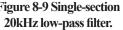

| 8.6 Multi-section Filters               |     |

| 8.7 Studying a New Filter with PSpice.  |     |

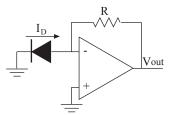

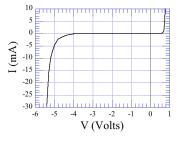

| Chapter 9: The Diode                    | 85  |

| 9.1 Introduction                        |     |

| 9.2 The ideal diode                     |     |

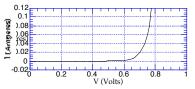

| 9.3 The Real Diode                      |     |

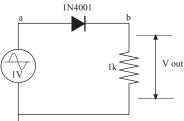

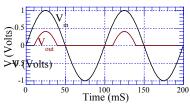

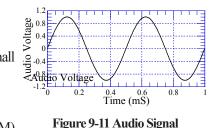

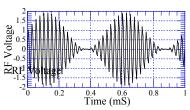

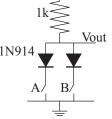

| 9.4 Some Common Diode Circuits          |     |

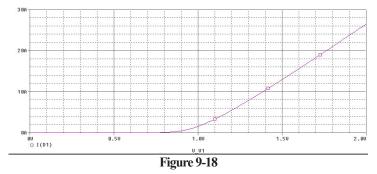

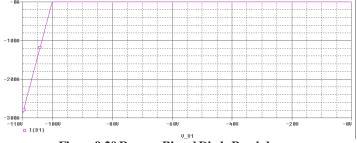

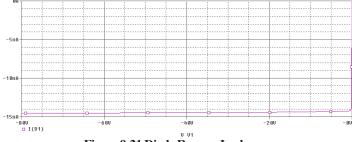

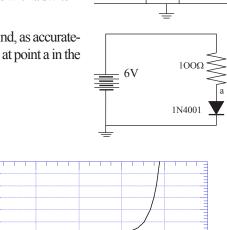

| 9.5 Diode Characteristics               |     |

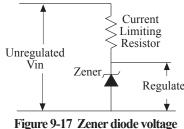

| 9.6 Special Kinds of Diode              |     |

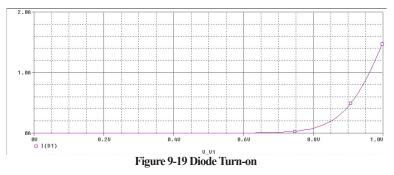

| 9.7 Using PSpice to Study a Diode       |     |

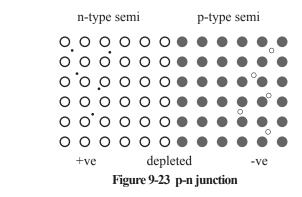

| 9.8 The Physics of Diodes               |     |

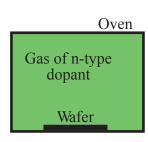

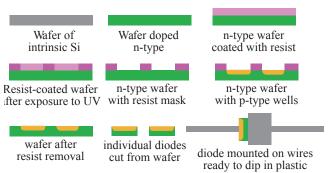

| 9.9 Manufacturing a diode               |     |

| ·                                       |     |

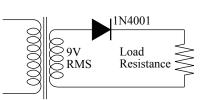

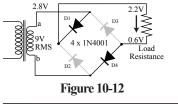

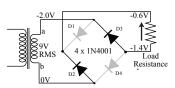

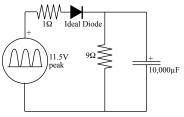

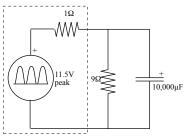

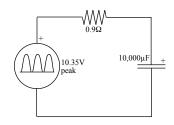

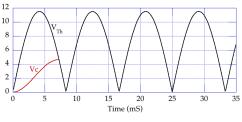

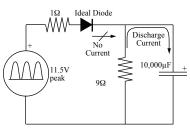

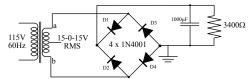

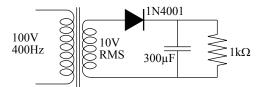

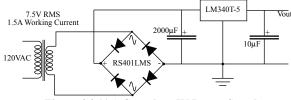

| Chapter 10:Power Supplies I             |     |

| 10.1 Introduction                       |     |

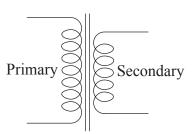

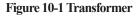

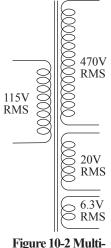

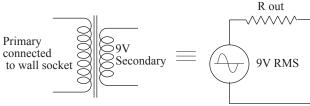

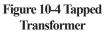

| 10.2 Transformers                       |     |

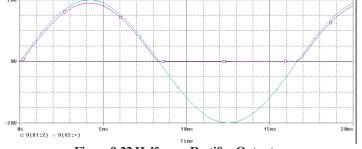

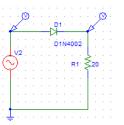

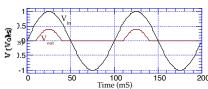

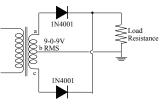

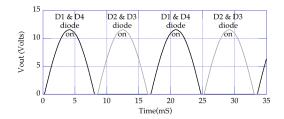

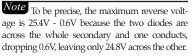

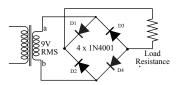

| 10.3 Rectifiers.                        |     |

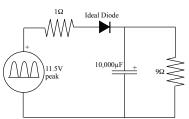

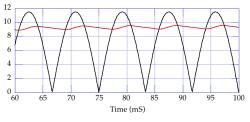

| 10.4 Smoothing the output               |     |

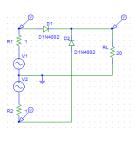

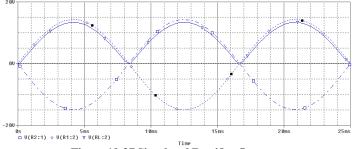

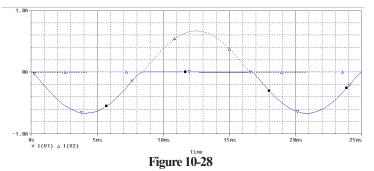

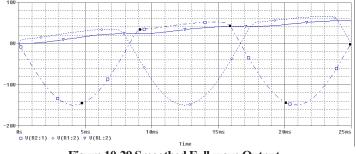

| 10.5 Simulating the Full-Wave Rectifier |     |

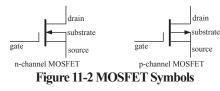

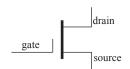

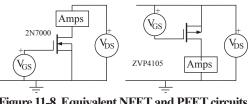

| Chapter 11: The Field-Effect Transistor |     |

| 11.1 Introduction                       |     |

| 11.2 The FET                            |     |

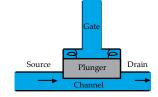

| 11.3 The water model MOSFET             |     |

| 11.4 3-terminal device characteristics  |     |

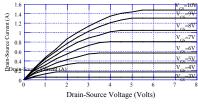

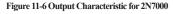

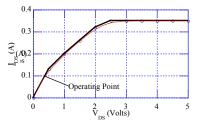

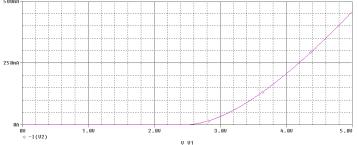

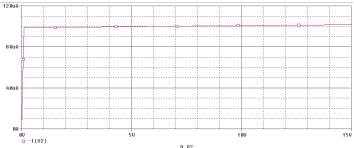

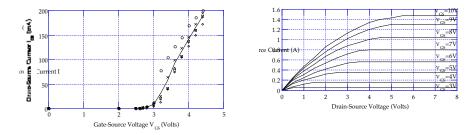

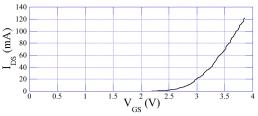

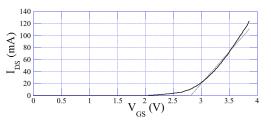

| 11.5 Characteristics of an FET          | 113 |

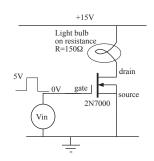

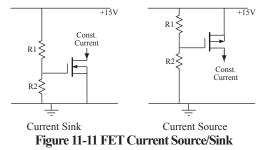

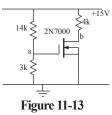

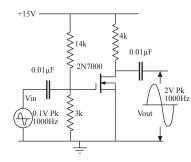

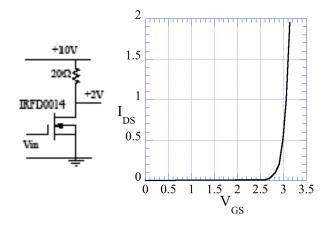

| 11.6 Simple FET circuits                |     |

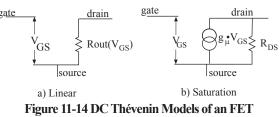

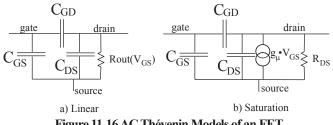

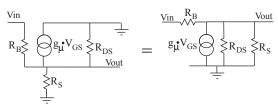

| 11.7 Thévenin Models of an FET          |     |

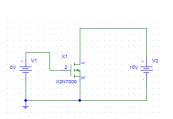

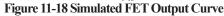

| 11.8 Using PSpice to Study a MOSFET     |     |

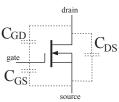

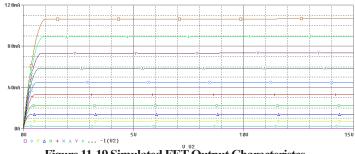

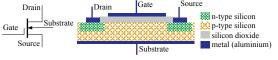

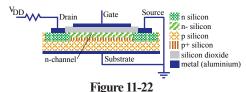

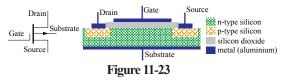

| 11.9 The Physics of FETs                |     |

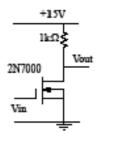

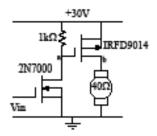

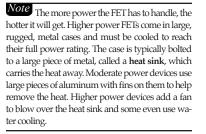

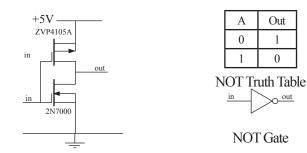

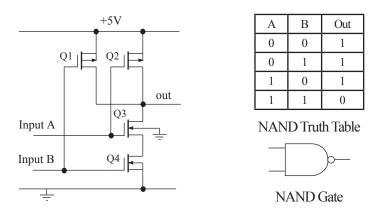

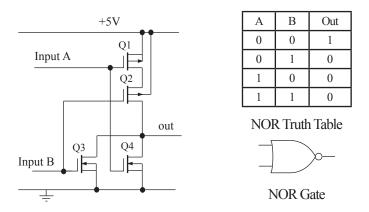

| Chapter 12:FET switches.                |     |

| 12.1 Introduction                       |     |

| 12.2 Power Switches                     |     |

| 12.3 Logic Switches                     |     |

| 12.4 FET Logic Switches                 |     |

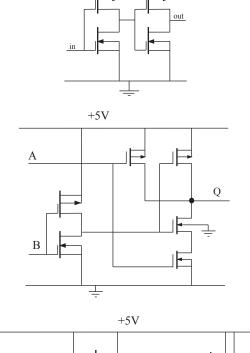

| 12.5 More complicated gates             |     |

| 12.6 Connecting Switches Together       |     |

| 12.7 Integrated Circuit Switches        |     |

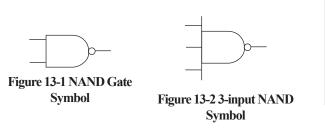

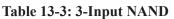

| Chapter 13:Digital Logic                |     |

| Theory                                  | 141 |

| 13.1 Introduction                       |     |

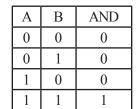

| 13.2 Truth Tables                       |     |

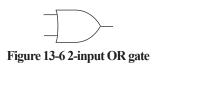

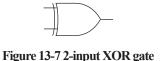

| 13.3 Some basic gates.                  |     |

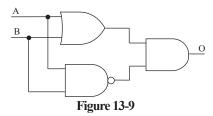

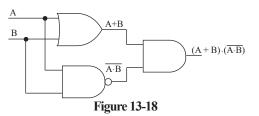

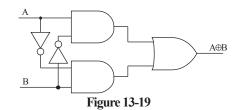

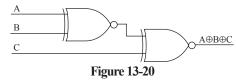

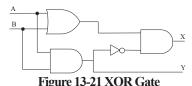

| 13.4 Multi-gate circuits                |     |

| 13.5 Boolean Algebra                    |     |

| 13.6 Logic simplification               |     |

| 13.7 Logic design                       |     |

| 13.8 Putting it all together            |     |

|                                         |     |

| Chapter 14: Combinatorial Functions-      |    |

|-------------------------------------------|----|

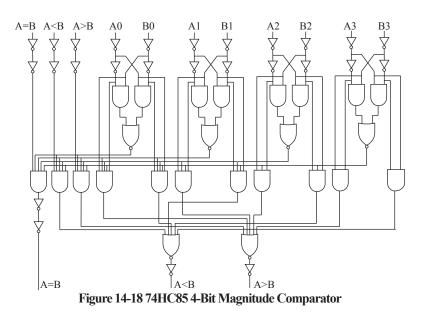

| 14.1 Medium Scale Logic                   |    |

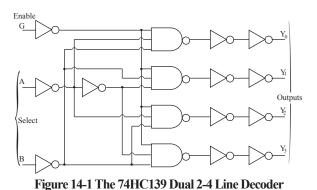

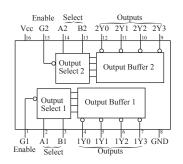

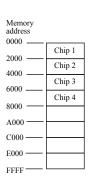

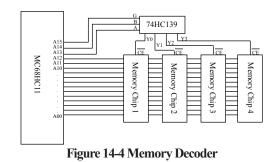

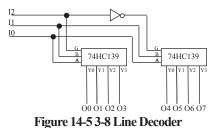

| 14.2 Coders/decoders                      |    |

| 14.3 Encoders                             |    |

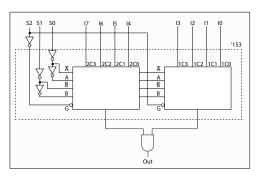

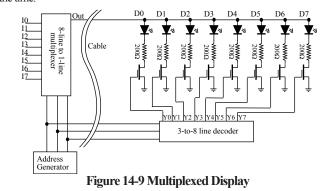

| 14.4 Multiplexers/demultiplexers          |    |

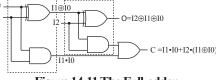

| 14.5 Arithmetic Logic                     |    |

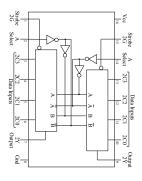

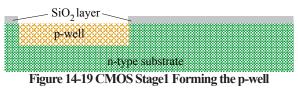

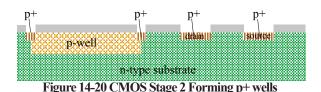

| 14.6 Building Digital Integrated Circuits |    |

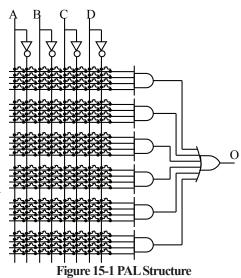

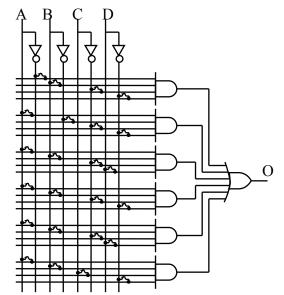

| Chapter 15:Programmable                   | 1. |

| Logic                                     |    |

| 15.1 Introduction                         |    |

| 15.2 The PAL                              |    |

| 15.3 The GAL                              |    |

| 15.4 Programming GALs                     |    |

| 15.5 A tutorial example using PALCMPL     |    |

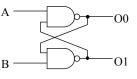

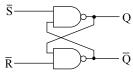

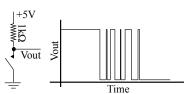

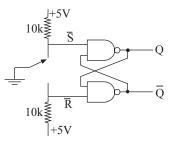

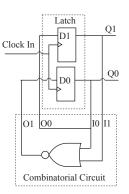

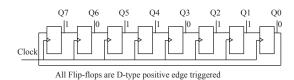

| Chapter 16:Sequential Logic               |    |

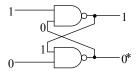

| 16.1 Introduction                         |    |

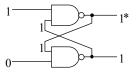

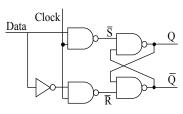

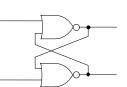

| 16.2 The Flip-flop                        |    |

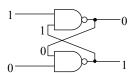

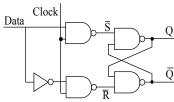

| 16.3 The transparent latch                |    |

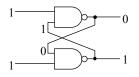

| 16.4 Logic diagrams for flip-flops        |    |

| 16.5 D-type flip-flops                    |    |

| 16.6 The J-K flip-flop                    |    |

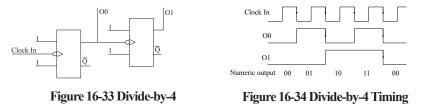

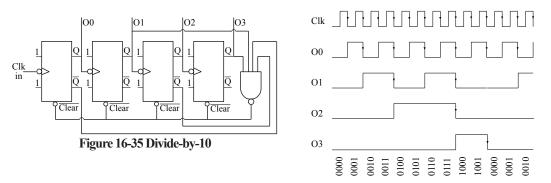

| 16.7 Simple counters                      |    |

| 16.8 Some other Chips                     |    |

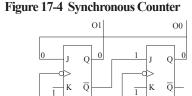

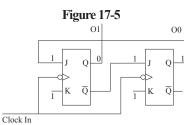

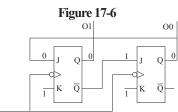

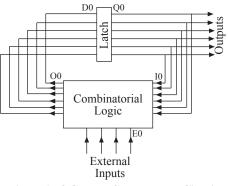

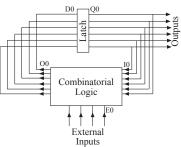

| Chapter 17:Synchronous Logic              |    |

| 17.1 Introduction                         |    |

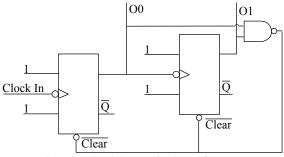

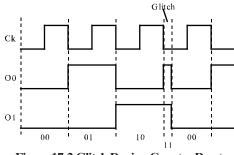

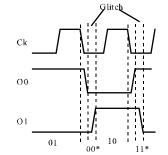

| 17.2 Glitches                             |    |

| 17.3 General Synchronous Systems          |    |

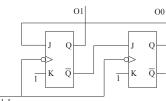

| 17.4 *J-K Synchronous                     |    |

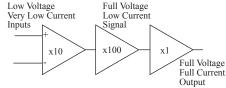

| Chapter 18: Amplifiers                    |    |

| 18.1 Introduction                         |    |

| 18.2 Gain                                 |    |

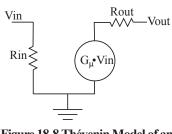

| 18.3 Thévenin Model of an Amplifier       |    |

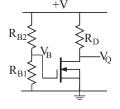

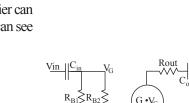

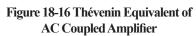

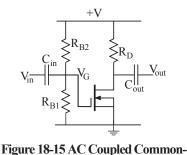

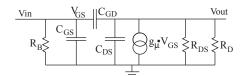

| 18.4 Common-Source FET Amplifier          |    |

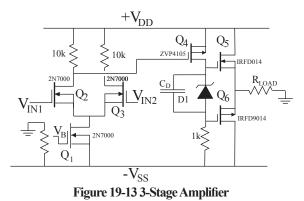

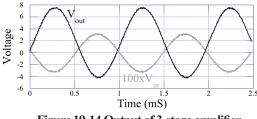

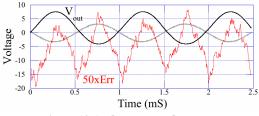

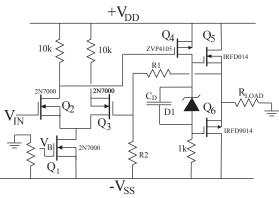

| Chapter 19:*Multi-Stage Amplifiers        |    |

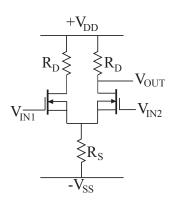

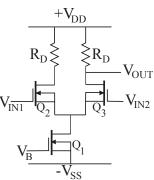

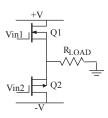

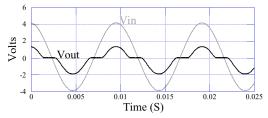

| 19.1 The difference amplifier             |    |

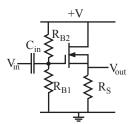

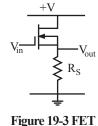

| 19.2 The FET Source Follower              |    |

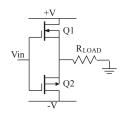

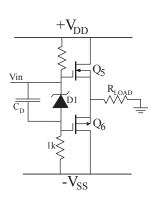

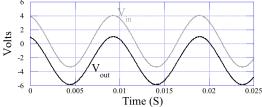

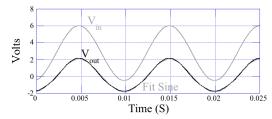

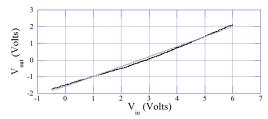

| 19.3 The Complementary Source Follow      |    |

| 19.4 A Complete Multi-Stage Amplifier     |    |

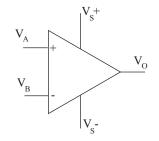

| Chapter 20: The Ideal Operational Am      |    |

| 20.1 Introduction                         |    |

| 20.2 The operational amplifier            |    |

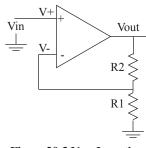

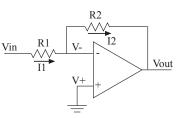

| 20.3 Feedback                             |    |

| 20.4 The non-inverting amplifier          |    |

| 20.5 The Golden Rules                     |    |

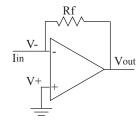

| 20.6 Virtual Ground                       |    |

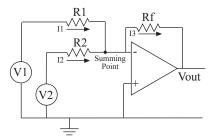

| 20.7 A few good circuits                  |    |

| Chapter 21:Real Op-Amps                   |    |

| 21.1 Introduction                         |    |

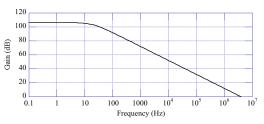

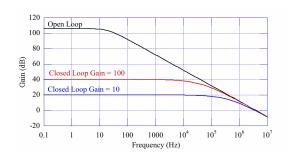

| 21.2 Frequency Response                   |    |

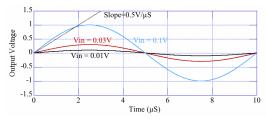

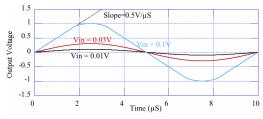

| 21.3 Output Current Limit                 |    |

157

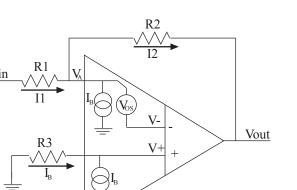

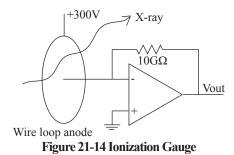

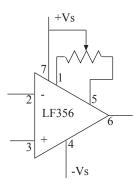

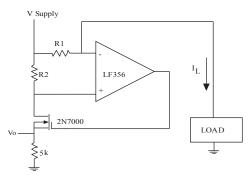

| 21.4 Input Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

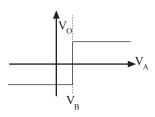

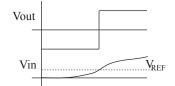

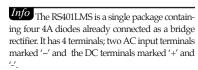

| Chapter 22:Comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

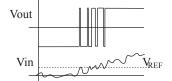

| 22.1 The Open-Loop Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

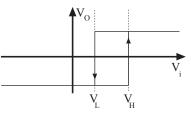

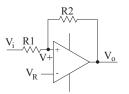

| 22.2 Hysteresis to the Rescue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                 |

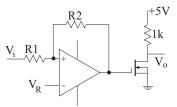

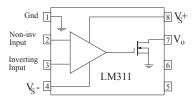

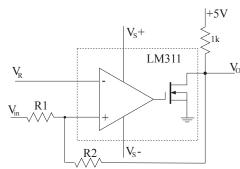

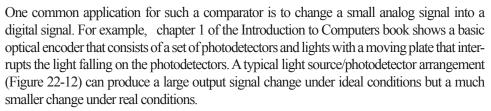

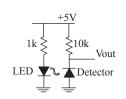

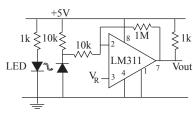

| 22.3 Commercial comparators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

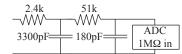

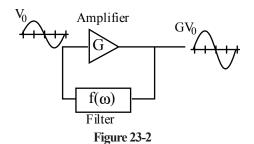

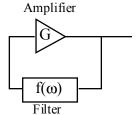

| Chapter 23:Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                 |

| 23.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

| 23.2 Linear Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |

| 23.3 Non-linear Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

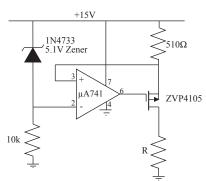

| Chapter 24:Linear Regulated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

| Power Supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |

| 24.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

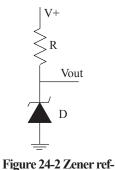

| 24.2 Voltage references.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                 |

| 24.3 IC references.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                 |

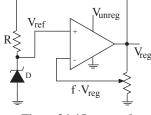

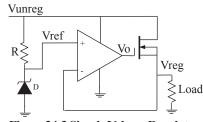

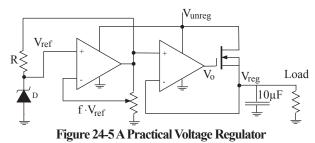

| 24.4 A simple voltage regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

| 24.5 Current regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |

| 24.6 IC voltage regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                 |

| 24.7 A complete power supply design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

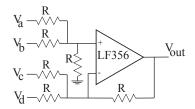

| Chapter 25:Digital-to-Analog Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |

| Chapter 25:Digital-to-Analog Conversion<br>25.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

| 25.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

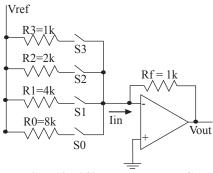

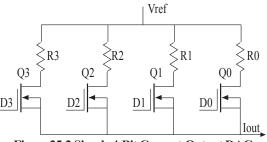

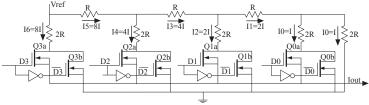

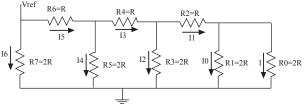

| <ul> <li>25.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 287<br>287<br>288<br>288<br>290                                                                                                                 |

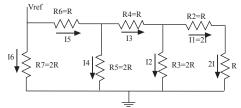

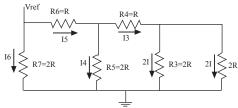

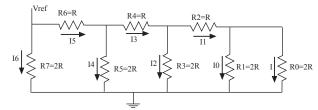

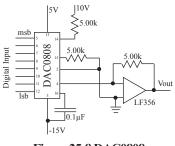

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                    | 287<br>287<br>288<br>290<br>291                                                                                                                 |

| <ul> <li>25.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 287<br>287<br>288<br>290<br>291                                                                                                                 |

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> Chapter 26:Analog-to-Digital Conversion                                                                                                                                                                                                                                                                                                                                            | 287<br>287<br>288<br>290<br>291<br>293<br><b>297</b>                                                                                            |

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> Chapter 26:Analog-to-Digital Conversion 26.1 Introduction                                                                                                                                                                                                                                                                                                                          | 287<br>287<br>288<br>290<br>291<br>293<br><b>293</b><br><b>297</b><br>297                                                                       |

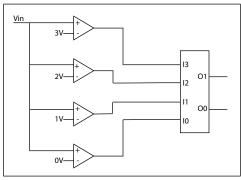

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> Chapter 26:Analog-to-Digital Conversion 26.1 Introduction 26.2 Flash Conversion                                                                                                                                                                                                                                                                                                    | 287<br>287<br>288<br>290<br>291<br>293<br><b>293</b><br><b>297</b><br>297<br>298                                                                |

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> Chapter 26:Analog-to-Digital Conversion <ul> <li>26.1 Introduction</li> <li>26.2 Flash Conversion</li> <li>26.3 A complete 3-bit flash ADC</li> </ul>                                                                                                                                                                                                                              | 287<br>287<br>288<br>290<br>291<br>293<br><b>297</b><br>297<br>298<br>298<br>298                                                                |

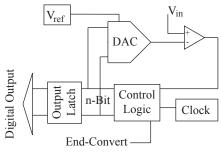

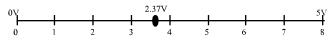

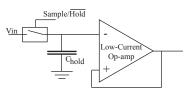

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> Chapter 26:Analog-to-Digital Conversion <ul> <li>26.1 Introduction</li> <li>26.2 Flash Conversion</li> <li>26.3 A complete 3-bit flash ADC</li> <li>26.4 Successive Approximation Conversion</li> </ul>                                                                                                                                                                            | 287<br>287<br>288<br>290<br>291<br>293<br><b>297</b><br>297<br>298<br>298<br>298<br>299                                                         |

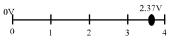

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> Chapter 26:Analog-to-Digital Conversion <ul> <li>26.1 Introduction</li> <li>26.2 Flash Conversion</li> <li>26.3 A complete 3-bit flash ADC</li> <li>26.4 Successive Approximation Conversion</li> <li>26.5 Imperfections of ADCs</li> </ul>                                                                                                                                        | 287<br>287<br>288<br>290<br>291<br>293<br><b>293</b><br><b>297</b><br>297<br>298<br>298<br>298<br>299<br>302                                    |

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> Chapter 26:Analog-to-Digital Conversion <ul> <li>26.1 Introduction</li> <li>26.2 Flash Conversion</li> <li>26.3 A complete 3-bit flash ADC</li> <li>26.4 Successive Approximation Conversion</li> <li>26.5 Imperfections of ADCs</li> <li>26.6 IC Converters</li> </ul>                                                                                                            | 287<br>287<br>288<br>290<br>291<br>293<br><b>293</b><br><b>293</b><br><b>297</b><br>298<br>298<br>298<br>298<br>299<br>302<br>302               |

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> Chapter 26:Analog-to-Digital Conversion <ul> <li>26.1 Introduction</li> <li>26.2 Flash Conversion</li> <li>26.3 A complete 3-bit flash ADC</li> <li>26.4 Successive Approximation Conversion</li> <li>26.5 Imperfections of ADCs</li> </ul>                                                                                                                                        | 287<br>287<br>288<br>290<br>291<br>293<br><b>293</b><br><b>293</b><br><b>297</b><br>298<br>298<br>298<br>298<br>299<br>302<br>302               |

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> Chapter 26:Analog-to-Digital Conversion <ul> <li>26.1 Introduction</li> <li>26.2 Flash Conversion</li> <li>26.3 A complete 3-bit flash ADC</li> <li>26.4 Successive Approximation Conversion</li> <li>26.5 Imperfections of ADCs</li> <li>26.6 IC Converters</li> </ul>                                                                                                            | 287<br>287<br>288<br>290<br>291<br>293<br><b>293</b><br><b>297</b><br>297<br>298<br>298<br>298<br>298<br>299<br>302<br>302<br>302<br>304        |

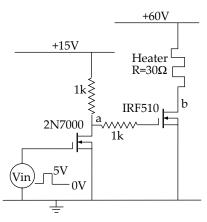

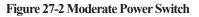

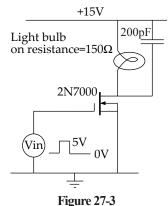

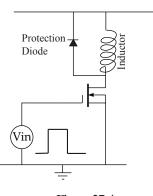

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> <b>Chapter 26:Analog-to-Digital Conversion</b> <ul> <li>26.1 Introduction</li> <li>26.2 Flash Conversion</li> <li>26.3 A complete 3-bit flash ADC</li> <li>26.4 Successive Approximation Conversion</li> <li>26.5 Imperfections of ADCs</li> <li>26.6 IC Converters</li> <li>26.7 ADC Examples</li> </ul> <b>Chapter 27:Power Switches</b> <ul> <li>27.1 Power Switches</li> </ul> | 287<br>287<br>288<br>290<br>291<br>293<br><b>293</b><br><b>297</b><br>298<br>298<br>298<br>298<br>299<br>302<br>302<br>302<br>304<br><b>309</b> |

| <ul> <li>25.1 Introduction</li> <li>25.2 The DAC</li> <li>25.3 The R-2R Ladder</li> <li>25.4 Commercial DAC chips</li> <li>25.5 Imperfections of DACs</li> <li>25.6 Some DAC examples</li> </ul> Chapter 26:Analog-to-Digital Conversion <ul> <li>26.1 Introduction</li> <li>26.2 Flash Conversion</li> <li>26.3 A complete 3-bit flash ADC</li> <li>26.4 Successive Approximation Conversion</li> <li>26.5 Imperfections of ADCs</li> <li>26.6 IC Converters</li> <li>26.7 ADC Examples</li> </ul>                                                                                 | 287<br>287<br>288<br>290<br>291<br>293<br><b>293</b><br><b>297</b><br>298<br>298<br>298<br>298<br>299<br>302<br>302<br>302<br>304<br><b>309</b> |

## **Chapter 1:Introduction**

We live our lives surrounded by electronic equipment. We are awoken by digital clock radios, strap digital watches on our wrists, eat breakfast in front of the television, travel to school or work listening to radios and CD players and then sit down in front of computers to do our work. On our way home, the iPod running loudly, we realize that we will be late and use our cell phones to call home. When we get home we eat food cooked in a microwave and then go surf the web for an hour or so before bed.

The scientist is even more surrounded by electronics. The chemistry lab is no longer mainly a place of gleaming glassware. Instead, it is full of electronic balances, pH meters, lasers, and NMR spectrometers. The biology lab has its spectrophotometers, more balances and pH meters, gas chromatographs, SDS gel systems, and electron microscopes. The geologist has electron microscopes, gas chromatographs, X-ray machines and seismographs while practically everything the physicist touches is electronic.

Many of the pieces of apparatus, both in the lab and in everyday life, are black boxes. We understand what they do; we may understand the principles by which they work; but we don't think we need to know the details of their circuits. However, only when we have a good knowledge of that circuitry that we can really appreciate what the instruments do and can understand their limitations.

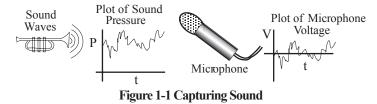

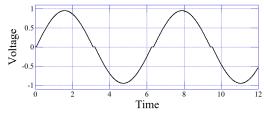

Consider the process of reproducing music using a CD. In the beginning, there were sound waves traveling through the air. A sound wave is rapid variation in the pressure of the air whose shape depends on the nature of the sound. Those sounds fell on a microphone that translated the varying air pressure into a varying voltage whose shape was just the same (Figure 1-1).

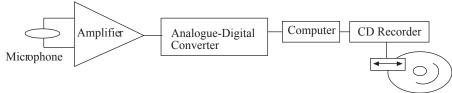

The microphone is a transducer. It translates the sound pressure information into voltage information, ideally without altering its shape at all. The voltage is then amplified and converted to a stream of numbers by an analogue-to-digital converter (ADC)

The ADC takes a voltage that is continuous in both time and space and samples it into a set of numbers that is discrete in both time and space. Obviously this means throwing away almost all of the information so we have to be careful to keep enough that our ears will not be able to tell that there is anything missing. That means that we have to take many samples per second (more than 40,000 samples per second) and we have to convert each one into a very accurate number, usually 16 bits long. The string of numbers representing the voltage is fed into a computer that performs some mathematical tricks to encode the information. Essentially, the computer adds extra copies of some of the information and then writes it to the CD as a pattern of flat and dented areas.

Figure 1-2 Making a Compact Disk

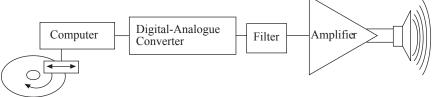

The CD player reads the pattern off the disk. This process is error prone so the computer in the CD player uses the extra information to correct the errors and reconstruct the original string

#### Chapter 1:Introduction

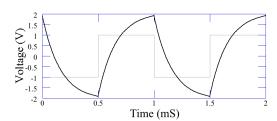

of numbers. The numbers themselves mean nothing to us so the computer in the CD player sends them to a digital-to-analog converter (DAC), which turns them back into voltages. The reconstructed signal is not quite the same as the original. Where the original was smooth, the copy consists of a lot of little steps so we pass it through a filter to remove the steps. Finally, the signal is amplified and converted back into sound by a loudspeaker, another transducer, and we hear it as sound.

Figure 1-3 Playing a Compact Disk

Most electronic devices follow a similar path. They measure something in the world, turning it into a time varying voltage called a signal. They process that signal in some way, extract information from it, and present that information to us. Table 1-1 gives some examples.

|                |                       | 1abic 1-1.                 | Some Fammar Electronic Devices                                                                           |                                                 |                            |

|----------------|-----------------------|----------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------|

| Instrument     | Input Signal          | Input Transducer           | Processing                                                                                               | Output Trans-<br>ducer                          | Output Signal              |

| CD Recorder    | Sound                 | Microphone                 | Digitize and Encode                                                                                      | Laser                                           | Light to burn pits in CD   |

| CD Player      | Light from CD<br>pits | Photo diode                | Decode, convert to analog and filter                                                                     | Loudspeaker                                     | Sound                      |

| Cell Phone     | Sound                 | Microphone                 | Amplify, digitize, modulate onto RF                                                                      | Antenna                                         | Radio Wave                 |

| Thermostat     | Temperature           | Thermistor                 | Compare actual temperature to preset limits, tak-<br>ing time of day into account, and turn heat on/off. | Switch                                          | Power to furnace or<br>A/C |

| Smoke Detector | Smoke and Fire        | Photodiode /Am<br>ion cell | Compare level with preset limits                                                                         | Siren                                           | Sound                      |

| pH meter       | ions in solution      | pH electrode               | Amplify signal, digitize, and display                                                                    | LCD display                                     | Visual image               |

| Television     | Radio Wave            | Antenna                    | Amplify, decode, split into sound and picture                                                            | Loudspeaker &<br>LED, LCD, or<br>plasma screen. | Image and Sound            |

**Table 1-1: Some Familiar Electronic Devices**

## **Chapter 2:Basic electrical** concepts

#### 2.1 The Properties of Charge

Electronics is the science of making electric charges do interesting and useful work, everything from lighting flashlights to running computers. At the heart of all electronics is the idea of electric charge. There are several ways of thinking about charge, some which are physically realistic and some which are not but which are very convenient because they use our physical intuition about how the world works. In the first half of the chapter we will take the very practical, unrealistic, view that is usually adequate for understanding electronics and leave the more physical view to the second half of the chapter, which can be omitted at a first reading.

#### 2.1.1 Charge

Although physics tells us that there are two kinds of electrical charge, which we call positive and negative charge, and that such charges come only in very small, indivisible packets, that detailed view of charges is very rarely needed to understand or design electronic equipment. Instead we can think of charge as an invisible kind of fluid that can move around inside certain kinds of materials, mostly metals. We refer to charge using the symbol Q and we measure the amount of charged fluid in units called Coulombs. One Coulomb is an arbitrary, fundamental unit in the same way that a meter is an arbitrary, fundamental unit of length-once you define that unit then you can make measurements. Using the unit, two people can compare measurements in a meaningful way but there is nothing that is special about the unit that you choose; reference amount with no particular physical it is merely a convenient tool.

We will think of charge as a kind of invisible fluid with certain properties-

- 1. You cannot make or destroy charge in any electronic apparatus; all you can do is to move gover station will generate tens of thousands of it around.

- 2. Charge can move around more or less freely within some materials (such as most metals Coulomb (compared to 3x10<sup>22</sup> water molecules in or salty water) but cannot move in or pass through other materials (such as air, wood, plastics, etc.). We call the materials through which current can pass Conductors and the ones through which it cannot pass Insulators.

- 3. When charge moves it does work, either useful work (such as lighting up your room) or useless work (such as the processor chip in a computer getting so hot that it has to have a fan or it will melt itself!).

- 4. When charge moves, it creates a magnetic field. When a magnetic field moves near a metal wire, it causes charge to move in the wire.

- 5. Charge comes in two kinds, positive and negative. If you mix the two kinds then they cancel each other out.

#### 2.1.2 Current

Moving charges form what we call Electric Current. We measure current by the amount of charge that passes a point in 1 second. The symbol for current is I and the unit of current is the use a few amperes of current; a vacuum might use Ampere-when a current of 1 Ampere is flowing, a charge of 1 Coulomb passed each point in 7A, a light bulb 1A, and a hair dryer 10A. Howev-1 second. We have the relationships

I=O/t and O=I×t

where Q is the charge passing a point in time t.

Info The Coulomb is named after the first person to measure the sizes of charges. The Coulomb meaning. Like the liter, the Coulomb is tiny when you think about a power station but treasonable when you think about a battery and enormous when you think about a single atom. A moderate Coulombs a second while a portable CD player may run for an hour or so on a single Coulomb. It takes 6x1018 elementary charges to make a single a liter of water).

Info The two different kinds of charge are extremely important in physics but they play very little role in electronics. In electronics we can almost always think of a single fluid that flows from the positive terminal to the negative and not worry about the real details.

Info Like the Coulomb, the Ampere is a moderate, every day, sort of unit. A typical appliance will er, we find an enormous range of currents in regular use. At one extreme, the US power grid carries millions of amperes around at any time and a bolt of lightning may carry tens of thousands of amps. At the other extreme, \$20 will buy us a component that can measure currents smaller than 1pA

In order to make charges move there must be a source of energy to act as a pump of the electrical fluid. The usual sources are either batteries, which convert chemical energy into electrical pumping action, or generators, which convert mechanical energy.

Because of property 1, electrical current can flow only in complete circles made of conducting materials, this gives rise to the term Electrical Circuit.

The simplest electrical circuit consists of a battery and a piece of wire as shown here in two different forms. In Figure, a is a sketch of the physical appearance of the system and b is a schematic diagram that uses symbols to show the way the circuit is connected but which ignores the physical appearance.

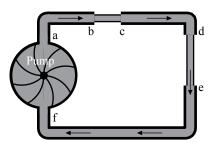

It can be very helpful to think of the charge as being like water, wires as being pipes, and batteries as being pumps. Using these ideas we can model our circuit as shown in Figure 2-2.

So long as the circuit is complete, the pump can keep the fluid circulating and the current flows. What happens if we disconnect the wire? A disconnected wire is not like a broken pipe-the electrical fluid cannot run out because air is not a conductor-instead it is like a blocked or closed-ended pipe. Now the fluid cannot flow past the blocked end and the current in the circuit is zero.

This analogy helps us understand what happens when we first connect a wire to a battery, before the circuit is complete. This is like connecting a closed end pipe to the pump while the inlet of the pump is blocked. In this case the pump will push water into the pipe until it reaches the blocked and then stop. There will be a very short-lived current and then a new equilibrium with no current flowing anywhere in the broken circuit.

As soon as we connect the free end of the wire to the other terminal of the battery, that is, we connect the end of the pipe to the inlet side of the pump, the current immediately starts to flow all round the circuit. Note that the current starts to flow immediately even though it may take several seconds for the first water that leaves the pump after the connection is made to get to the end of the pipe.

#### 2.1.3 Voltage

The only way to make water flow round a set of pipes is to exert a force or more properly a pressure, on it. Similarly, the only way to make an electrical current flow in a circuit is to exert and electrical pressure on it. We call that electrical pressure Electric Potential and we measure it in units of Volts.

Electrical potential, like pressure in a fluid system, is a relative quantity-we can only measure the potential difference between two points in a circuit. Thus an instrument for measuring potential, a Voltmeter, has two terminals (usually colored red and black) and measures the potential difference between the terminals. If the pressure tries to push charge into the red terminal and out of the black one then we say the potential difference is POSITIVE and if the pressure tries to push the charge into the black terminal and out of the red then the potential difference is NEGATIVE. In order to make a measurement you MUST connect both terminals of the meter because it can only measure the potential difference between two points.

ing from the positive terminal of a battery to the Having said that, in practice we often speak of voltage at a point in the circuit, just as we often speak of the pressure at a point in a fluid system. We can do this by fixing on a single point tion. Fortunately we hardly ever have to worry in the circuit as a reference and making all measurements between that point and the point of interest as shown below. This means that the point is automatically at zero volts since the potential difference between that point and itself must be zero. We call this point ground and it is usually chosen to be at the negative terminal of the battery or other voltage source powering the circuit.

Figure 2-1 Wire and Battery Circuit

Figure 2-2 Water Model of a Circuit

Info We can measure current in several ways. The most common way is to pass the current through a small resistor and measure the voltage across the resistor with a sensitive electronic voltmeter. Older instruments pass the current through a small coil and use the magnetic field that it generates to move a needle. All of these instruments have to be inserted into the circuit. There are also instruments that can measure the current flowing in a wire without breaking the circuit to insert the instrument. They measure the small magnetic field that the current sets up round the wire.

Note Although we normally speak of conventional current, a current of positive charges flownegative terminal, in practice current is carried by negative electrons traveling in the opposite direcabout this. We will stick to general practice and use conventional current

#### 2.1.4 Power

When current flows it does work, either usefully or producing waste heat. We call the rate at which work is done power. The power dissipated in an electronic device depends on both the amount of current that flows and on the voltage driving it according to the formula

P=I×V

where I is the current through the component and V the voltage drop across it.

We measure energy in Joules and power in Watts.

1 Joule = 1 Watt  $\cdot$  1 sec or 1 Watt = 1 Joule /1 Sec

so a current of 1 Amp flowing through a potential difference of 1 Volt generates a power of 1 Watt and so does work at the rate of 1 Joule per second.

#### Example\_

A radio that draws 30mA = 0.03A of current from a 9 volt battery uses energy at a rate of P=0.03A×9V=0.27Watts.

#### 2.1.5 Resistance

A potential difference causes a current flow. In the mid 19th century Georg Ohm found that, for most common materials under normal conditions, the amount of current that flows is proportional to the voltage difference that makes it flow. If we double the driving voltage then the current flowing will double, if we halve the driving voltage then the current halves In such a material, we can make a graph of the relationship between the current flowing and the voltage drop making it flow. The graph will be a straight line like that in Figure 2-3.

0.8 (Amperes) 0.6 0.4 0.2 0 5 10 15 20 V (Volts) Figure 2-3 I-V plot for a linear resistance

1

This kind of graph, called an I-V curve, is one of the most useful tools for describing the behavior of electronic components. This is the simplest kind, a straight line. A component with this behavior is called a Linear Component and a circuit made up only of linear components is a Linear Circuit. Notice that we plot I as a function of V and not the other way round because in most circuits we directly control the applied voltage (for example, we choose the battery) and then we measure the current that results.

Such a component system is described mathematically by the relationships

#### $V \propto I$ or $V = k \times I$

where the constant of proportionality, k, is a characteristic of the particular circuit. We call the constant Resistance (symbol R). This linear relationship is called Ohm's Law and it can be written in several different forms depending on what information we have and what we want to know. If we know the current flowing in a known resistor and want the voltage across the forms of Ohm's law. You write the law in a triangle resistor then we use

#### V=I×R

If we know the voltage across the resistor and we know its value then we can find the current  $\frac{(circled in the figure)}{(circled in the figure)}$  then you are left with V/R so that I = V/R as shown in the figure. flowing through the resistor using

#### I=V/R

Finally, we can find the resistance if we know the voltage and the current using

R=V/I

The unit of resistance is called the **Ohm**, symbol  $\Omega$ , A resistor of 1 Ohm lets through 1 Ampere when there is 1 Volt across its terminals.

#### Example.

For example, if we connect a  $220\Omega$  resistor across the terminals of a 1.5V battery then we can find the current that flows in the resistor using the second form of Ohm's law.  $I = V/R = 1.5V / 220\Omega = 0.0068A = 6.8mA$

as shown in Figure 2-4. Then, to find any one term, you cover that term up with a finger and what is left is the formula. So, e.g., if you cover up the I

Figure 2-4 Ohm's Law

Note The Joule is another of our standard units of measurement. It is the amount of energy that it takes to lift a 1 kg mass through a vertical distance of 10 cm. It is thus a fairly small unit of energy. For example a small container of yogurt supplies about 920,000 Joules of energy! The Watt is a similarly small unit of power. A single electric light bulb uses 60-100 Watts of power; a hairdryer about 1000-1200 Watts. Another common unit of power is the HorsePower. 1 HorsePower = 750 Watts.

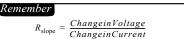

The resistance, R, is related to the slope of the line on the I-V graph but beware; it is not itself the slope. Instead, we have

$$Slope = \frac{\text{Change in I}}{\text{Change in V}} = \frac{I}{V} = \frac{1}{R}$$

so that  $R = \frac{1}{\text{Slope}}$

Thus a nearly horizontal line corresponds to a very HIGH resistance while a nearly vertical line corresponds to a very LOW resistance.

#### Example.

The current through the resistor shown in Figure 1-6 changes by 1A when the driving voltage changes by 20V. The slope is Change in I 1A1

Start =

$$\frac{1}{\text{Change in V}} = \frac{1}{20V} = 0.05 \times \frac{A}{V}$$

so that  $R = \frac{1}{0.05} = 20\Omega$

#### Remember

The voltage in Ohm's law is the voltage across the resistor; the difference between the voltages at the two ends.

#### Example.

If one end of a  $100\Omega$  resistor is at 4.5V above ground and the other end is at 2.3V above ground then the voltage across the resistor is 4.5V - 2.3V = 2.2V so that the current through the resistor is  $I = 2.2V/100\Omega = 22mA.$

#### 2.1.6 Power in resistors

The voltage drop V across a resistor that is passing a current I causes the current to do work on the resistor so that power is dissipated. This power causes the resistor to heat up and we call the effect Joule Heating. Because Ohm's law relates the current and voltage in a resistor, we can calculate the power dissipation if we know only the voltage and the resistance or only the current and the resistance. If we apply a voltage V to a resistance R then a current I = V/Rflows so that the resistor dissipates power at the rate of

$$P = I \times V = I \times V/R = V^2/R$$

Similarly, if a current I flows through a resistor R then there must be a voltage V=I×R across the resistor and so it must dissipate power

$$P=I \times V=I \times I \times R=I^2R$$

Example\_

which means that

so that

A loudspeaker has a resistance of  $8\Omega$ . Calculate the voltage that must be applied to make it dissipate 10 Watts of power.

Since we know the power and resistance, we can say  $10W = V^2/8\Omega$

$V^2=10W \times 8\Omega = 80Volts^2$

V=√80=8.9V

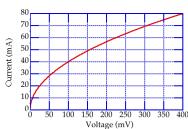

Figure 2-5 Non-linear Resistance I-V

2.1.7 Non-linear resistances

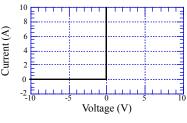

There are some components that have I-V curves that are not straight lines. These are called non-linear components and they require that we extend our idea of resistance to take account of these more general cases. Look at the I-V graph of Figure 2-5. This is the I-V curve for a small light bulb. Obviously, no single value describes this resistance, but it can still make sense to talk of resistance at different applied voltages, if we are careful about how we do it. There are two different ways to define the resistance of a non-linear component. Both are useful in different ways.

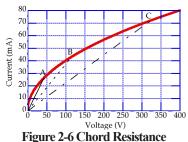

The simpler of the two, sometimes called the chord resistance, is useful if you want to find the total current that will flow when a given voltage is applied. To find the chord resistance, we just apply Ohm's law directly to the straight lines as in Figure 2-6.

The chord resistance is not used very often; usually you would just use the curve itself to find the current at a given voltage.

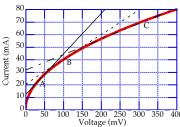

The more useful resistance is called the **slope resistance** and is important when you want to know how small changes in the applied voltage will affect the current. First, look at what happens when we make small changes in the voltage across a linear resistor. We know that

V=I×R

so if we increase V by an amount  $\Delta V$  then a new current flows. We shall write the new current as the sum of the old current I and some small change in I, I, produced by that change. Then Ohm's law says

$V + \Delta V = (I + \Delta I) \times R$

If we subtract the original V from both sides we are left with

$\Lambda V = \Lambda I \times R$

So, for a linear resistance, we get exactly the same resistance value if we write Ohm's law in terms of the changes as when we write it in terms of the voltage and current. We use this equation as the definition of the slope resistance, often called r rather than R.

$r=\Delta V/\Delta I$ Now we can apply this to our non-linear resistance. The slope resistance is  $r = \frac{1}{\text{Slope of tangent line at point of interest}}$

By drawing tangent lines carefully, we can measure the values of the resistance at various points as shown in Figure 2-7.

#### Example\_

At point A in Slope Resistance, the solid tangent line runs from =0V, I=12mA to V=225mV, I=80mA so we have

ΔV=0.225V-0V=0.225V and ΔI=0.08A-0.012A=0.068A

so the slope resistance is

$r=\Delta V/\Delta I=0.255/0.068=3.3\Omega$ .

At point C the dashed tangent line runs from V=0V, I=32mA to V=0.38V, I=80mA giving us a slope resistance r=0.38/(0.08-0.032)=0.38/0.048=7.9Ω

### 2.2 The physics of current flow

Everything in nature is made up of atoms and the atoms themselves are made up of still smaller particles. At the heart of every atom (Figure 2-8) is an incredibly tiny ball of mass and charge called the nucleus. Inside the nucleus there are two kinds of particle, some of them have no charge and are called neutrons, some carry a positive charge and are called protons. Flying round the nucleus is a cloud of negatively charged electrons, one electron for each proton in the nucleus.

Every charged particle carries round with it an electric field, an intangible thing that affects proximation of reality. First, the nucleus is so small any other charge that comes into it. The field round a positively charged particle acts on other 10 millionths of the radius of the atom) that it could positive charges to push them away but it acts on negative charges to pull them in towards the particle. The field around a negatively charged particle acts in reverse, attracting positive where the electrons are so drawing well-defined charges and repelling negative ones. The forces that these fields exert are enormously power- orbits is misleading. Since we can't draw anything ful, strong enough to hold the electrons in orbit around their atomic nuclei and to glue atoms together into molecules. For example, the electric force between two protons is 10<sup>36</sup> times as the years and don't try to interpret them too literlarge as the gravitational force between them.

Electrostatic forces would dominate the universe if there were only one kind of charge. Instead, the positive charge on the proton is exactly the same size as the negative charge on the electron; a complete atom has no net charge. The positive and negative charges exactly cancel charges are negative and half positive. Put several and there is no electric field to affect the world outside the atom. Since almost all matter is electrically neutral, the electric forces that play such a large role in the atomic world are not of mass. important for objects as large as us.

Figure 2-7 Slope Resistance

Figure 2-8 Semi-classical Atom

Note Any picture like this can only be a poor apcompared to the total size of the atom (only about not be seen on the same scale. Second, quantum mechanics says that you can't ever really know much closer to the reality we stick to images that give our minds a view that has proved useful over Info The existence of two kinds of charge that cancel each other out makes the electric field very different from the gravitational field. Put several charges together and on average you have a weaker electric field because on average half of all masses together and you always have a stronger gravitational field because there is only one sign

#### 2.2.1 Solids

At room temperature the atoms of most elements stick together with electric forces to make rigid arrays of atoms, solids. There are many kinds of solid. Some kinds are made up of regular arrays of one, or a few, kinds of atoms. We shall mostly be concerned with these crystalline solids. Other kinds are made up in a much more complex fashion. First the atoms join together into large assemblies called molecules and then the molecules form arrays that make up the solids. A substance such as wood has an enormously complex structure in which arrays of molecules make up fibers and then these fibers are held together by other kinds of molecules. Since complex molecular solids are almost always non-conductors we shall not be concerned with them.

A crystalline solid is built from regularly repeating, rigid blocks of atoms. In an elemental solid such as pure copper all the atoms are the same. In a compound solid, such as table salt, there may be several kinds of atom but they come in groups and all the groups are identical Figure 2-9.

| 0 | 0                                     | 0          | 0 | 0 | 0 | 0 |  | 0 | • | 0 | • | 0 | • | 0 |

|---|---------------------------------------|------------|---|---|---|---|--|---|---|---|---|---|---|---|

| 0 | 0                                     | 0          | 0 | 0 | 0 | 0 |  | • | 0 | • | 0 | • | 0 | • |

| 0 | 0                                     | $\bigcirc$ | 0 | 0 | 0 | 0 |  | 0 | • | 0 | • | 0 | • | 0 |

| 0 | 0                                     | 0          | 0 | 0 | 0 | 0 |  | • | 0 | • | 0 | • | 0 | • |

| 0 | 0                                     | 0          | 0 | 0 | 0 | 0 |  | 0 | • | 0 | • | 0 | • | 0 |

| 0 | 0                                     | 0          | 0 | 0 | 0 | 0 |  | • | 0 | • | 0 | • | 0 | • |

|   | Elemental Solid Compound Solid        |            |   |   |   |   |  |   |   |   |   |   |   |   |

|   | Figure 2-9 Atomic Structure of Solids |            |   |   |   |   |  |   |   |   |   |   |   |   |

Inside most compound solids the atoms are very, very tightly attached to their electrons. You can apply a voltage to the solid and the electrons stay put; no current flows. They are insulators. Inside most elemental solids, in particular inside the metals, a few of the electrons are much less tightly bound. These electrons are called the conduction electrons. There are usually one or two of them to each metal atom and they can be pulled away from their parent atoms by an electric field.

If we put a metal crystal in an electric field then the electrons in the metal will move around. We get an idea of how this happens in the following figures.

Figure 2-10 shows the metal crystal before we apply an external field. Each atom is shown as a little blob with a circle and a dot round it. The blob is the atomic core-the nucleus and those electrons that are tightly bound to it. The circle is the orbit of the single loosely bound conduction electron and the dot is that electron.

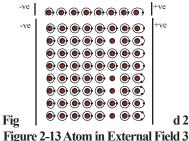

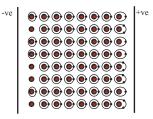

InFigure 2-11, the crystal has been placed in the external electric field. The field has distorted the electronic orbits. This is shown schematically in the picture by the expansion of the orbits on the positive side of the field and the contraction on the negative side. The field is pulling the electrons towards it.

Figure 2-11 Atom in External Field 1

In Figure 2-12 the electric field is stronger. Now the distortion is large enough that a few of the electrons in the second column jump into the oversize orbits in the last column. This leads to a few extra electrons in the far right column and leaves behind some atoms without outer electrons in the second column. These atoms have orbits for electrons but no electrons to put in them. Such an orbit without an electron is called a hole. Note that the atoms with holes have a positive charge so that the hole behaves a little like a positive particle.

As Figure 2-13 shows, the previous situation is unstable. The second column holes pull on the d2 electrons on either side of them. Those to the right are held by the external field but those to the

Figure 2-10 Atom in Zero Field

left are not and so electrons have jumped from the third row into the second. Now the second row is happy but the third row has atoms with holes.

Obviously, the holes are no more stable in the third column than they were in the second. Thus, electrons move from the fourth row to fill the holes, then electrons move from the fifth row into the fourth and so on. As the electrons move from left to right, the holes appear to move from right-to-left until they end up in the left most column. At the end, there are extra electrons at the right edge, which has a negative charge, and some orbits with holes at the left-hand edge, which has a positive charge (Figure 2-14). The whole process takes only a matter of nanoseconds.

We have seen how charges can move around inside a metal as electrons jump from atom to atom and holes move in the other direction. So far, this has been a transitory process with charges building up on the surfaces of the solid and current flowing for a very brief time. If we connect wires (other pieces of metal in which the same processes are going on) to the crystal then we can bleed off the extra electrons on from the right and supply electrons from the left Figure 2-14 Atom in External Field 4 so that a steady current flows. That current is carried in the same way, with electrons hopping Note This description of what the electrons do through the metal lattice leaving holes into which other electrons can jump.

#### 2.2.2 Resistance

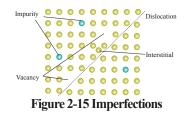

In a perfect crystal the electrons can hop from atom to atom without any loss of energy; current have minds that don't work that way and so we flows with no voltage loss. This phenomenon is called superconductivity and it is observed in electrons. So long as we don't take the details of the a number of materials at very low temperatures. Most real crystals at room temperature contain various kinds of imperfection. There are impurities, atoms of the wrong kind, and atoms operates. out of place in various ways as we see in Figure 2-15.

Even if there are no impurities or displaced atoms, the individual atoms are rarely in exactly the right places because they jiggle around. When an electron tries to jump to an out-of-place atom or to an incorrect atom it has problems. The effect is that the electron loses a little bit of energy. That means that the outside world has supply energy to keep the current flowing; there has to be a voltage to pump the current through the material. The more electrons are trying to get through the crystal at any time, the more energy it takes to push it through. This is the origin of Ohm's law. Even more, the higher the temperature is, the more the atoms jiggle around. That means that the atoms are more out of place at high temperatures and the resistance is higher.

#### 2.2.3 Semiconductors

Towards the right hand side of the periodic table there are a few elements that sit on the border between the conductive metals and the insulating non-conductors, elements such as selenium, germanium, and, most important, silicon. The outer electrons in these solids are more tightly bound to their atoms than those in the metals but not quite so tightly as those in non-metals. These materials are called semiconductors. Very pure semiconductors, called intrinsic semiconductors, are insulators under normal conditions. However, if small amounts of impurities are added to the crystal, it can be made to conduct. By controlling the impurities, we can make semiconductor devices with a wide range of fascinating properties. These semiconductor devices, such as diodes, transistors, and integrated circuits, lie at the heart of modern electronics. They are the amplifiers and switches that make all our electronic gadgets work.

Let us examine the conduction mechanism in silicon, by far the most important of the semiconductors. Each atom of silicon has four electrons in its outer orbit but they are too tightly bound to move around in the crystal. If we can knock a few electrons out of their places then they can move around in the silicon. It takes quite a lot of energy to knock an electron out of its orbit and the only source of energy is the thermal motion of the atoms. At room temperature the thermal energy available is so low that there are very few of these conduction electrons around. Indeed the electron density in a pure semiconductor is about 10<sup>-12</sup> times the density in a conductor. Thus, although these electrons are free to move, they can carry very little current

is only a model. Quantum mechanics tells us that we should not really think of individual electrons but should describe how waves of electron probability act within the solid. However, most of us use models to gain insight into the behavior of the models too literally, these models can give us a useful working insight into the way the atomic world

and the material is almost an insulator. As you warm the crystal up, there is more energy available to knock electrons out but even at 100°C there are too few electrons around to carry any significant current. So we have a material with almost no moveable electrons (or holes) but one in which electrons (and thus holes) can move around quite easily.

If we apply an electric field to a piece of semiconductor, that is we put a voltage across it, then there is an extra source of energy. If the electric field is strong enough then it can pull electrons out of their orbits and drive them through the crystal. However, the fields needed to do this are very large compared to the usual fields that we encounter in most devices. Only in rather special circumstances do you find fields that are strong enough to pull electrons out of their orbits and make them conducting electrons. However, those circumstances do occur in some semiconductor devices as we shall see in chapter 12.

If we add a very tiny amount of an element that is similar in size to silicon, then the new atoms can take the place of a very few of the silicon atoms without altering the structure of the crystal. If we add in an element that has five electrons in its outer orbit, such as phosphorus, then we get a crystal with a few sites that have too many electrons but are otherwise very similar to their neighbors. Something very interesting happens. The extra electrons are very loosely bound to their parent atoms and can hop around. They can't hop from impurity to impurity because the impurities are much too far apart, but the nearby silicon atoms are sufficiently similar that they can accept an extra electron for a little while and then pass it on. Thus the impure semiconductor can conduct by passing the extra electrons along through the crystal. This is called an n-type semiconductor because it has extra negative charges that carry the current. We say that the semiconductor has been doped with the impurity and call the impurity a donor impurity because it donates extra electrons to the bulk crystal.

If we use as our impurity an element such as aluminum, with only three electrons in its outer orbit, then we get impurity sites that have one electron too few. Each impurity atom has a hole where the fourth electron should be. It is very easy for an electron from a nearby silicon atom to fall into the impurity site and so make the hole jump from the impurity onto the silicon. Again, we have introduced some free charges that can carry current around, if we apply an electric field to move them. We call such a material a p-type semiconductor because it conducts with positive holes. We call the impurity an acceptor because it accepts electrons from the silicon crystal to leave behind mobile holes.

Note that there is one very important difference between conduction in a metal and in a doped semiconductor. In a metal there are potentially at least as many charge carriers as there are atoms so there is no practical limit to the current that can flow. In a semiconductor there are only as many charge carriers as impurities. Since only about 1 in  $10^6$  atoms is an impurity there is a much lower limit to the maximum current that can flow. It is quite possible to saturate a semiconductor, that is to reach a point at which the current cannot increase no matter how high you raise the voltage because you have run out of charge carriers.

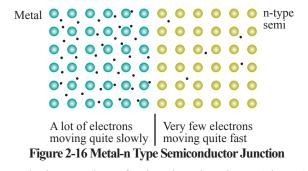

If we connect a metal wire to a piece of n-doped semiconductor (Figure 2-16) then we can get electrons to cross the junction very easily. The metal has floods of conduction electrons available and can pass them around quite freely. At a junction between an n-type semiconductor and a metal these electrons pass freely across the junction and current flows from metal to semiconductor or vice versa. In the semiconductor, the current is carried by a very small

number of electrons moving quite rapidly. In the metal, there are enormously more electrons around and so they move along much more slowly to carry the same current.

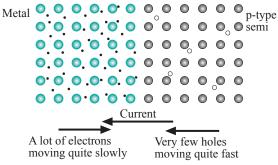

At a junction between a p-type semiconductor and a metal, things are a little more interesting. If the current is flowing from the semiconductor to the metal then the holes are flowing towards the metal (Figure 2-17). At the junction, each hole eats up an electron from the metalthat is an electron from the metal falls into the hole. This means that more electrons must flow from the metal toward the junction. So the electrons and holes both flow towards the junction, where they destroy each other.

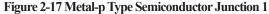

If the current flows from the metal to the semiconductor then the electrons in the metal are flowing away from the junctions (Figure 2-18). That means that electrons are being sucked out of the semiconductor, creating holes. The holes migrate through the semiconductor carrying the current with them. Thus the electrons and holes both migrate away from the junction, the holes widely spaced and moving quickly, the electrons tightly packed and moving slowly.

#### Summary

Electronics deals with movement of **charge**, Q, measured in **Coulombs**. When charge moves it forms a **current**, I, measured in **Amperes**.

I=Q/t and 1 **Ampere** = 1 Coulomb per second Current is driven by electrical pressure or **potential**, V, measured in Volts. When a charge Q moves through a potential difference V it does work, W, measured in **Joules**.

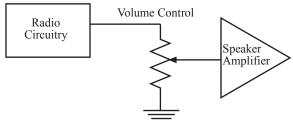

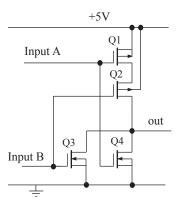

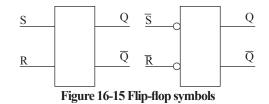

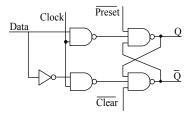

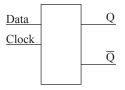

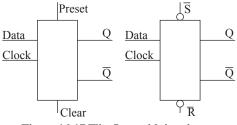

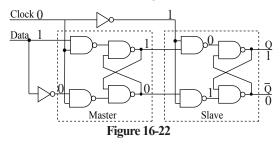

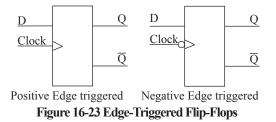

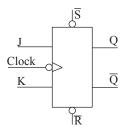

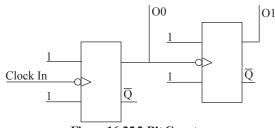

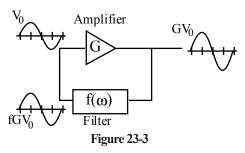

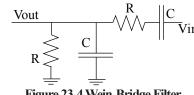

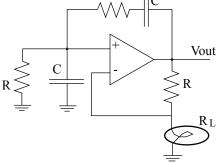

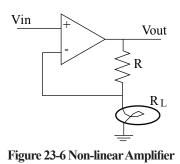

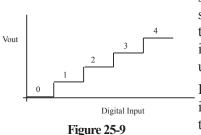

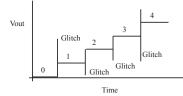

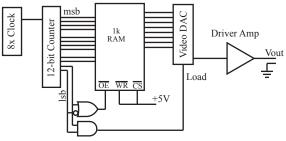

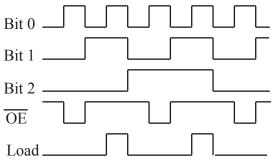

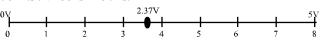

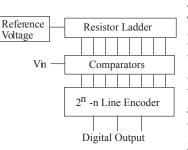

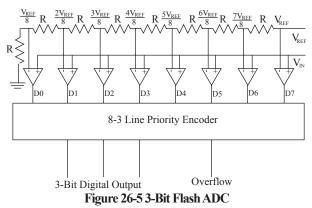

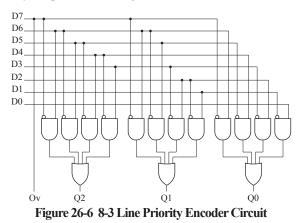

W=Q×V and 1 Joule=1 Coulomb×1 Volt