My First Design

The first thing that I want to try to make is a serial adder. My interest was inspired by the design of the Manchester Mark I computer and I was surprised when a similar design was the focus of Chapter 2 in Navabi's book. There are some differences, however

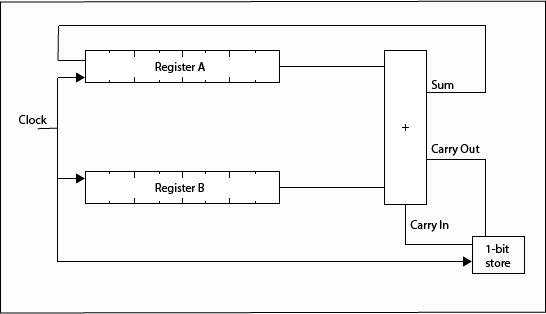

I want to mimic one small part of a real computer as best I can, except that I am using an 8-bit word rather than the 32-bit word of the Mark I. I chose this simply to reduce the amount of testing needed. It is easier to plough through 8 bits of output than 32. So my adder starts with two numbers held in 8-bit registers, for now I will call then A and B, and ends with the sum in A and with B unchanged. Navabi's design starts with two numbers entered serially directly into the adder and stores the output into a register.

The basic idea is to shift the numbers, one bit at a time, out of the righthand end of the registers into the adder. This produces a sum bit and a carry bit. The sum needs to be fed back into register A and the carry saved for addition into the next bit.

We will have to augment and refine this to reach a final design but this is our basic structure. It would actually be possible to write a Verilog behavioral simulator for this as it stands (and we would find the problems with it!) but I find this a perfectly useful way to describe the design in its own right. Instead, I will start to look at the building blocks that we have identified and try to write Verilog code for them.