Debugging the Adder

So what is wrong with the flip-flop. I start by looking at the sadd2.v code, concentrating on the set and reset lines to the flip-flop.

// // Serial adder built from modules that realize available // bits of hardware. // The register are dual 74194s defined as // module psregister(sin, pin, clk, mode, reset, pout, sout); // Full adder is defined as // module fadd(a, b, cin, q, cout); // Flip-flop is one element of a 7474 // module dflop74(d, clk, set, reset, q, qbar); // Note that all the set and reset lines are active low. module sadd(inA, inB, modeA, modeB, clk, rst); /* Declare input and output wires */ input [7:0] inA, inB; input [1:] modeA, modeB; input clk, rst; wire inA, inB, modeA, modeB, clk, rst; /* Intermediate wires */ wire [7:0] value1; wire [7:0] value2; wire q1, q2, cin, cout, sout; wire set = Supply1; /* and then the net itself */ psregister r1 (sout, inA, clk, modeA, rst, value1, q1); psregister r2 (q2, inB, clk, modeB, rst, value2, q2); fadd a1(q1, q2, cin, sout, cout); dflop74 f1(cout, clk, set, reset, cin); endmodule // sadd |

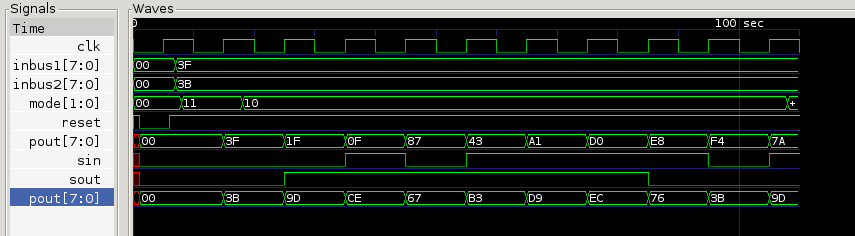

Well, I am not sure about set but reset is clearly problematic. The input to the module is rst and the input to dflop74 is reset so it is no wonder they didn't work! Fixing that typo improved things and lead me to a typo in the register where a right shift did not bring in the serial input. Looking carefully at the code I realized the I was using a wire for the set input to the dflop where I needed a reg. Switching to a reg made the flip-flop work correctly and everything improved. I looked carefully at the output and made one more change, asking for 9 clock cycles instead of 8. That got me to this output.

Now we see that by the end register A (the first pout) has reached the correct value (0x3f+0x3B=0x7A) but register B has gone past its correct value of 0x3B to 0x9D.

At this point the serial add Verilog is working correctly but the control sequencing in the test bench is slightly off. It says that we need separate mode controls for the two registers.I will look at that next but first I want to include the corrected serial add Verilog.

// // Serial adder built from modules that realize available // bits of hardware. // The register are dual 74194s defined as // module psregister(sin, pin, clk, mode, reset, pout, sout); // Full adder is defined as // module fadd(a, b, cin, q, cout); // Flip-flop is one element of a 7474 // module dflop74(d, clk, set, reset, q, qbar); // Note that all the set and reset lines are active low. module sadd(inA, inB, modeA, modeB, clk, rst); /* Declare input and output wires */ input [7:0] inA, inB; input [1:] modeA, modeB; input clk, rst; wire inA, inB, modeA, modeB, clk, rst; /* Intermediate wires */ wire [7:0] value1; wire [7:0] value2; wire q1, q2, cin, cout, sout; reg set = 1; /* and then the net itself */ psregister r1 (sout, inA, clk, modeA, rst, value1, q1); psregister r2 (q2, inB, clk, modeB, rst, value2, q2); fadd a1(q1, q2, cin, sout, cout); dflop74 f1(cout, clk, set, rst, cin); endmodule // sadd |