Putting It All Together

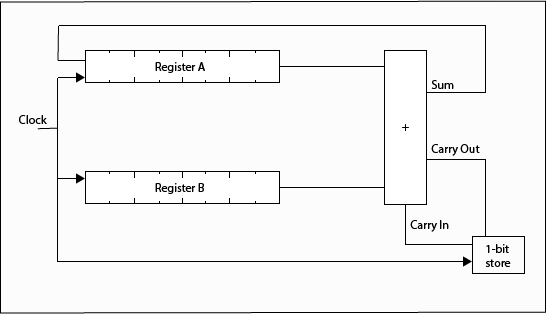

We now have all the pieces that we need to instantiate our serial adder. Let's remind ourselves of the design and remember that the goal is to implement A = A + B, leaving B unchanged.

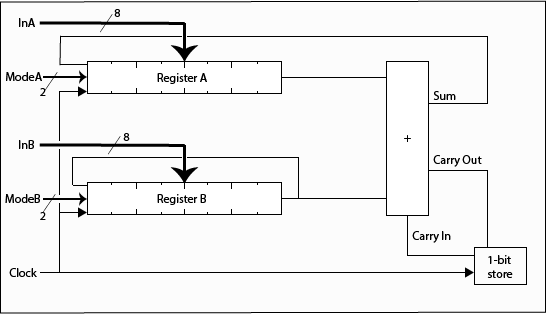

With some experience in hand we can now identify one clear problem with this design. We have not indicated any way to get data into the registers to start with. Fortunately, we chose to use registers with a parallel load capability. In fact our registers not only need their parallel inputs but they also need a 2-bit mode input to control their behavior upon receiving a clock. We can augment our diagram to show these. We can also realise that register B needs something to connect to its serial input otherwise its contents will become undetermined. Since we want B to end up the same as it started we will connect its input to its output and let its contents recirculate. We get

Note the use of thickened lines with slashes to indicate multi-bit signals. So we have a new module that has five inputs and no output (more on that later). It is easy to write since it consists entirely of wiring together our existing modules.

// // Serial adder built from modules that realize available // bits of hardware. // The register are dual 74194s defined as // module psregister(sin, pin, clk, mode, reset, pout, sout); // Full adder is defined as // module fadd(a, b, cin, q, cout); // Flip-flop is one element of a 7474 // module dflop74(d, clk, set, reset, q, qbar); // Note that all the set and reset lines are active low. module sadd(inA, inB, modeA, modeB, clk, rst); /* Declare input and output wires */ input [7:0] inA, inB; input [1:] modeA, modeB; input clk, rst; wire inA, inB, modeA, modeB, clk, rst; /* Intermediate wires */ wire [7:0] value1; wire [7:0] value2; wire q1, q2, cin, cout, sout; wire set = Supply1; /* and then the net itself */ psregister r1 (sout, inA, clk, modeA, rst, value1, q1); psregister r2 (q2, inB, clk, modeB, rst, value2, q2); fadd a1(q1, q2, cin, sout, cout); dflop74 f1(cout, clk, set, reset, cin); endmodule // sadd |